LAPORAN AKHIR 2

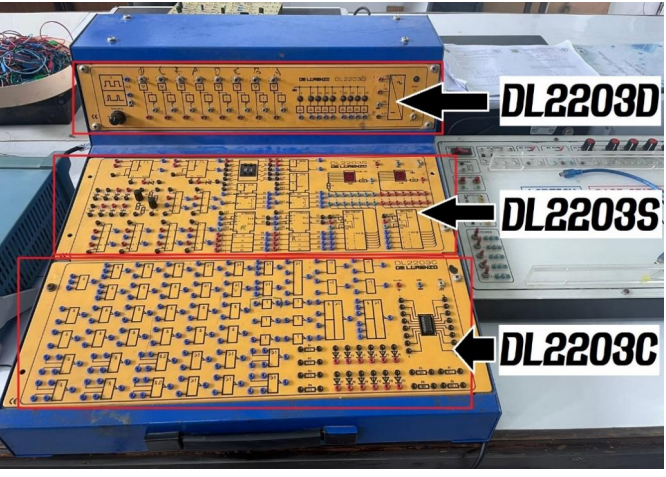

2. Alat dan Bahan [Kembali]

2.2 Bahan Proteus

1. IC 74LS112

Gambar 3. IC 74LS112

2. Switch (SW-SPDT)

Gambar 4. Switch

3. Logicprobe atau LED

Gambar 5. Logic Probe

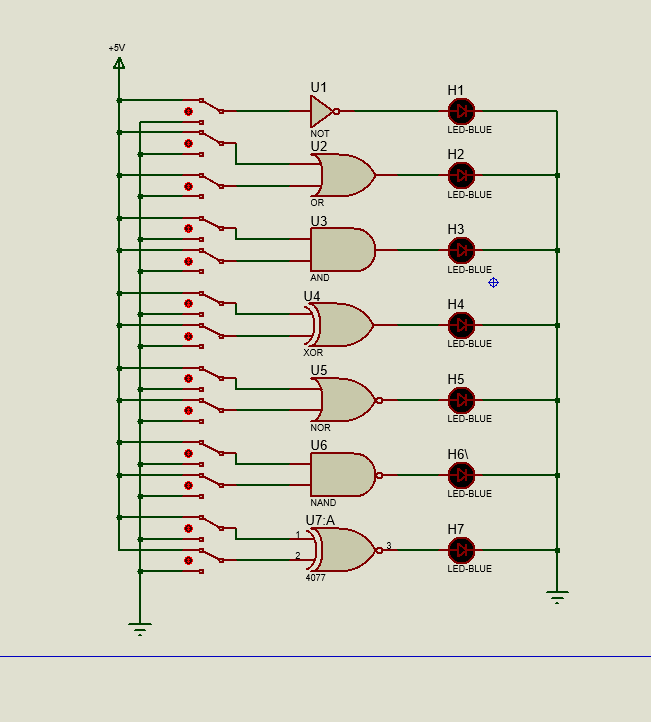

3. Rangkaian [Kembali]

.png)

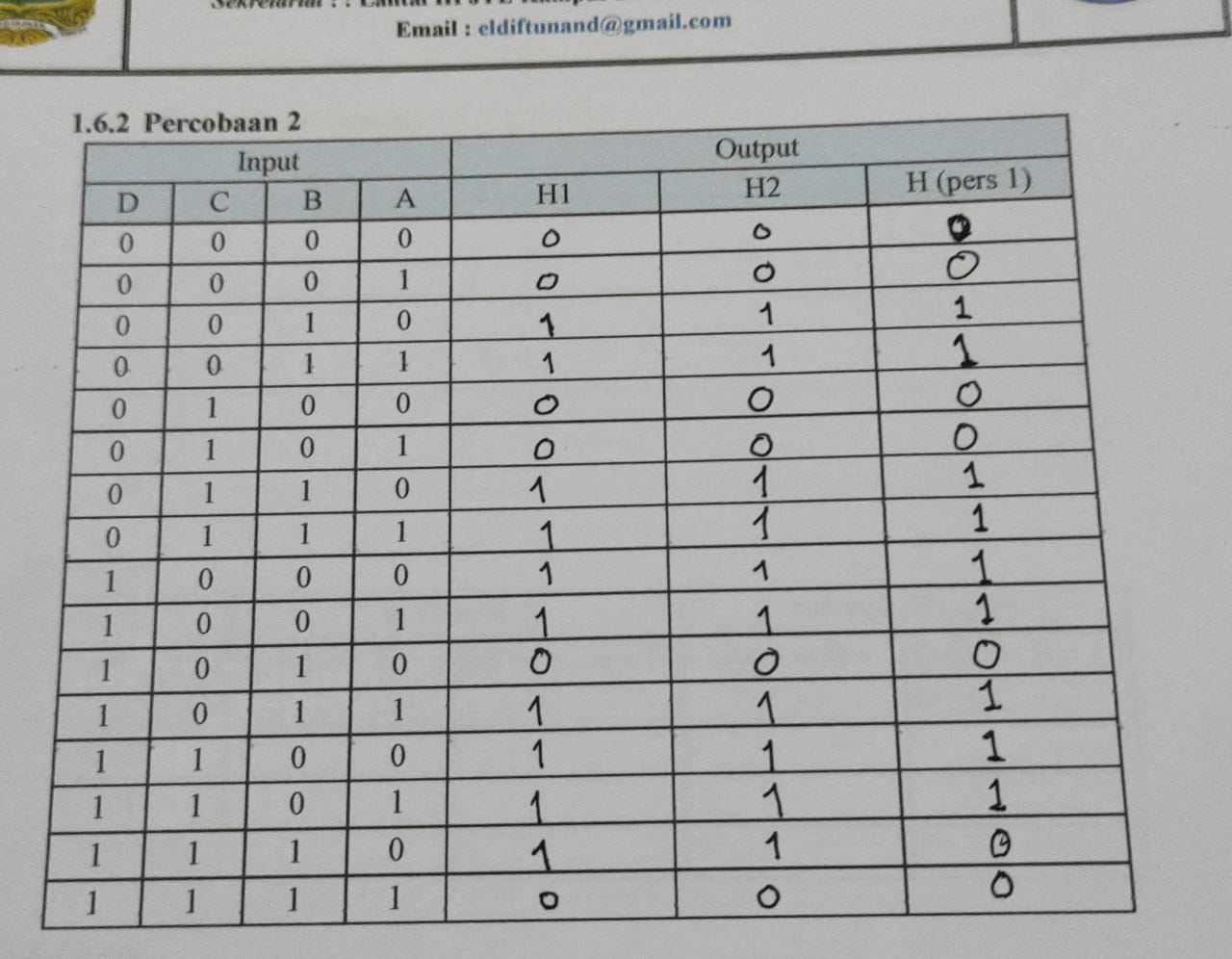

percobaan 2 kondisi 6

percobaan 2 dengan input B0=0 B1=clock B2=1 menggunakan T flip-flop

dalam percobaan menggunakan T flip flop dimana T flip-flop sendiri merupakan rangkaian JK yang dimana input J dan K nya dihubungkan menjadi 1 sehingga inputnya menjadi 1 yaitu T. dalam percobaan input T dihubungkan langsung ke VCC sehingga logika bernilai 1 pada input T, sedangkan pada input R dan S aktif low dihubungkan dengan B0 dan B2 dengan logika pada input yang diberi 0 dan 1 , sehingga input yang dibaca adalah logika 1 untuk B0 dan 0 untuk B2 karena input nya adalah activ low.

hasil pembacaan akan diambil dari sifat asinkronus karena input R dan S sedang aktif dan JK dan clock diabaikan , seperti pada modul yang berlogika 1 saat pembacaan adalah R dan S berlogika 0 sehingga yang tampil di input Q adalah 0 dan Q' adalah 1 , Q bernilai 0 berarti reset aktif , sedangkan jika 1 artinya set.

6. Analisa [Kembali]

1. Apa yang terjadi bila B1 diganti clock pada kondisi 2

=

Jika B1 dihubung clock dengan logika 0 maka B2 adalah dont care dan B0 adalah 1, karena B2 di set dan B0 di reset maka jika B2 berlogika 1 maka dia masuk ke kondisi sinkron dan jika B2 0 maka masuk ke asinkron dimana keluaran nya adalah set 1 dan Q'=0

2. Bandingkan hasil percobaan dengan teori

=

Percobaan berfokus pada kondisi asinkron karena inp T dihubungkan langsung ke vcc dan yang diatur adalah S-R , dimana dapat diambil hasilnya percobaan sesuai dengan teori dengan kondisi sinkron dan asinkron juga sifat input actif low (fall time) dan actif hight (rise time)

3. Apa fungsi kaki pada flipflop yang digunakan

=

T = merupakan input yang dimana dalam t adalah kaki J dan K yang dihubungkan

CLk = kaki ini berfungsi untuk mengatur clock

R = kaki input reset dimana jika kaki ini aktif maka Q akan bernilai 0

S = kaki input set dimana jika kaki ini aktif maka Q akan bernilai 1

Q dan Q' = kaki output dimana aslinya kaki Q' adalah invers Q

7. Download [Kembali]

File HTML [download]

File Gambar Rangkaian 1 [download]

File Video Rangkaian 1 [download]

File Rangkaian Percobaan 1 Kondisi 8 [download]

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)